What Is Routing In VLSI Physical Design?

- Darshini M B

- September 9, 2023

Routing in VLSI is making physical connections between signal pins using metal layers. Following Clock Tree Synthesis (CTS) and optimization, the routing step determines the exact pathways for interconnecting standard cells, macros, and I/O pins. The layout creates electrical connections using metals and vias that are determined by the logical connections in the netlist (i.e; logical connectivity converted as physical connectivity).

CTS has information on all the cells, blockages, clock trees, buffers, inverters, and I/O pins that have been put in. The Routing program uses this data to electrically complete all of the connections defined in the netlist , ensuring that there are no DRC violations. The tool makes all the connections defined in the netlist in a way that:

- The design is completely routed

- There are minor LVS violations and SI breaches

- There should be no or few congestion hotspots

- The timing DRCs and QOR are met

Mechanism of Routing in VLSI:

The routing mechanism establishes the specific pathways for interconnections. This contains the regular cell and macro pins, block boundary pins, and chip boundary pads. The tool includes information about the exact placements of blocks, pins of blocks, and I/O pads at chip borders after placement and CTS. The utility can also access the logical connections defined by the netlist. Metal and vias are used in the routing stage to build electrical connections in layout to fulfill all connections required by the netlist. The program now depends on some “Design Rules Checks (DRC)” to perform the natural linkages.

What are the steps of routing in VLSI?

Each metal layer in a grid-based routing system has its tracks and preferred routing direction, which are described in a unified cell in the standard cell library. Routing activities are divided into four steps:

- Global route

- Track Assignment

- Detail Routing

- Search and repair

Global Route:

Global routes assign nets to particular metal layers and global routing cells. The global route aims to avoid crowded global cells while making as few diversions as possible. Global routes also avoid pre-routed P/G, placement, and routing bottlenecks.

Track Assignment (TA):

It allocates each net to a certain track and lays down actual metal traces. To reduce the number of vias, it attempts to create long, straight lines. At this stage, physical DRC is not considered.

Detail Routing:

Detail Routing seeks to repair any DRC violations following track assignment using a set size small region (SBox). The detailed routing goes through the whole design box by box until the routing pass is finished.It also performs timing driven routing .

Search and Repair:

This resolves any remaining DRC breaches using many iterative loops with progressively bigger SBox sizes.

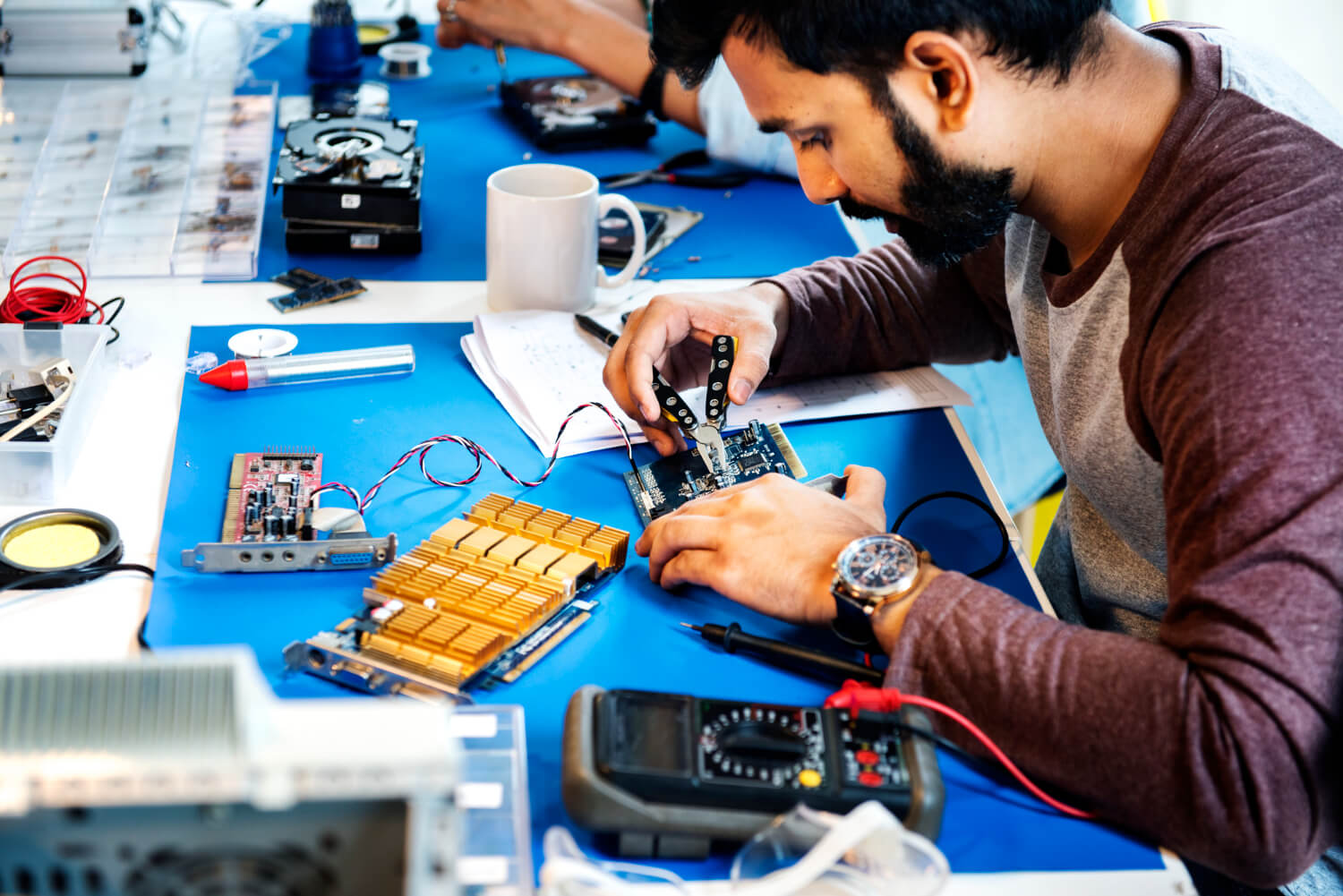

If you want to learn more new things about VLSI design, enroll yourself in one of the online VLSI courses here at Chipedge, the best VLSI training institute in Bangalore . It offers a wide range of VLSI design courses including design verification courses , RTL design courses , etc. Contact us to know more.

Share This Post:

Exploring the Nexus of VLSI vs Embedded Systems: Unraveling the Intricacies

Best Practices for the Physical Design of IoT Solutions

Marvelous Microchip: The role of VLSI in Computers

Fabrication process in VLSI

How to Become a VLSI Engineer?

What is Latch Up in VLSI and Its Prevention Techniques?

Trending blogs.

Lint in VLSI Design and its importance in RTL Design

Role of Machine Learning in VLSI design

What is metastability in vlsi and how to avoid it.

Exploring the Expansive Landscape of VLSI Applications

Blog categories.

- Analog Layout (9)

- ASIC Design Flow (2)

- Design for Test (29)

- Design Verification (27)

- General (65)

- Internship (17)

- Physical Design (39)

- RTL Design – Lint & CDC (7)

- SOC Design (1)

- Synthesis & STA (2)

Course Categories

VLSI Courses for Professionals

VLSI Courses for Freshers

Online VLSI Courses (Self Paced)

VLSI Programs for Enterprises

Flat 40% off on all courses, subscribe to our blog.

- Hiring Companies

- Placement Details

Associate With Us

- Refer & Earn

- Be Our Trainer

- Be Our Guest Blogger

For Enterprises

- Corporate Training

Programs Offered

- Formal Verification

- ASIC Design Verification

- Design For Test

- Physical Design

VLSI Courses for Students & Freshers (UG/PG)

- Privacy Policy

- Refund Policy

- Terms & conditions

Get Upto 40% OFF

IMAGES

VIDEO

COMMENTS

Track Assignment (TA): It allocates each net to a certain track and lays down actual metal traces. To reduce the number of vias, it attempts to create long, straight lines. At this stage, physical DRC is not considered. Detail Routing: Detail Routing seeks to repair any DRC violations following track assignment using a set size small region (SBox).